実験の目的

FETによる電圧増幅作用を確認します。

実験にあたっては、小信号増幅を前提として、FETを線形な素子として

近似して解析します。そして、この方法で求めた回路の増幅度と

入出力インピーダンスが、実験から得られた測定値と一致することを確認し、

回路設計の際に定量的な議論が出来るようにします。

実験課題

- 直流動作点

- 電圧増幅度

- 出力インピーダンス

- 入力インピーダンス

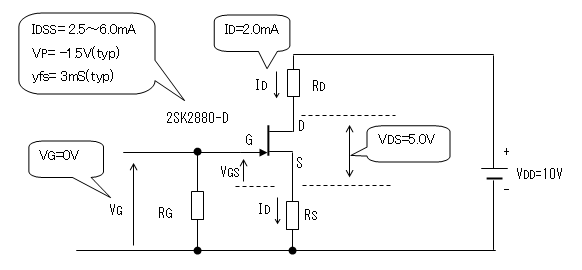

実験に使用するFETは、N-チャネルタイプの2SK2880-Dを使います。

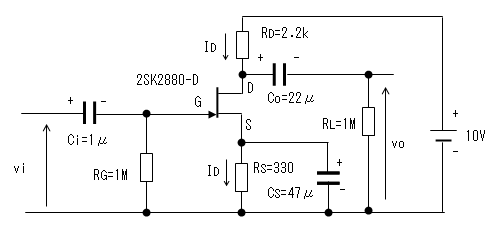

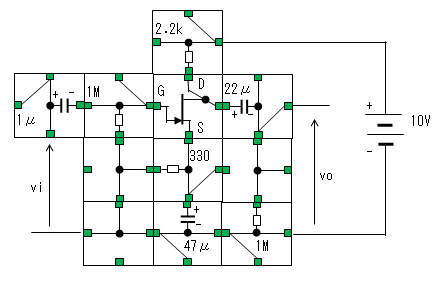

実験回路

出力側に接続した抵抗器:RLは、出力電圧の直流レベルを確定するために

接続しました。この抵抗がないと、電源投入時、出力コンデンサ:Coの電荷が0であるため、

出力波形の直流レベルが浮き上がることから、オシロスコープで波形を見る場合見づらいです。

今回は交流信号に対してRL接続の影響が出ないように、RL >> RDとなる

値を選定しました。

回路の動作

FETに(近似的な)線形動作をさせるためには、まず バイアス電圧をかけ動作点を決めます。 バイアス回路は自己バイアス回路を用いており、

バイアス点を安定化しています。

入力信号はゲート(G)に印加します。ソース(S)の抵抗RSにはパスコンCSが

並列に接続されているため、ソースは交流的にはグランドと同電位です。

そこで、入力信号Viを入力すると、

↓

Viはゲート〜ソース間の電圧変化vgsとなる。

↓

ドレイン電流idがvgsのgm倍されて変化する。

↓

idの変化がRDの両端の電圧VDの変化⊿VDとなる。 その値は⊿VD = id * Ro。

ここで、Ro = RD//RL。

↓

⊿VDの変化は出力voとして取り出される。

ちなみに、パスコンCSがあると交流的には負帰還がかかりません。

実験回路の設計

- 設計条件

-

(1)電源(VDD)は10Vとします。

(2)FETは2SK2880のDランクを使う。(データシートよりIDSS=2.5〜6.0[mA])

設計にあたってはIDSS = 4.0[mA]で計算します。

(3)ドレイン電流(ID)はIDSSの1/2に設定する。 よってID = 2.0[mA]

(4)ドレイン〜ソース間電圧VDS: 5[V] (=VDDの1/2)

(5)増幅する周波数帯域の最低周波数は50Hz

(6)入力側(信号源)の出力インピーダンスは130[Ω]

(7)出力側(負荷)の入力インピーダンスは1MΩ

- バイアス回路の設計

- RSの選定 設計条件(2)とすると、回路構成より、あとは使用するFETのyfs

- RDの選定 RDは次の式で与えられるので

- RGの選定 ゲートの電位を0[V]にする目的の抵抗ですが、FETのゲート(G)には電流が

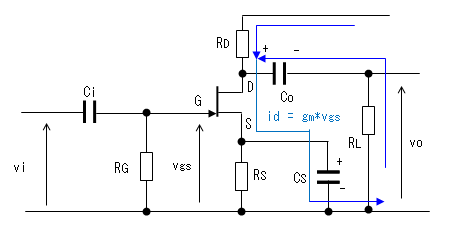

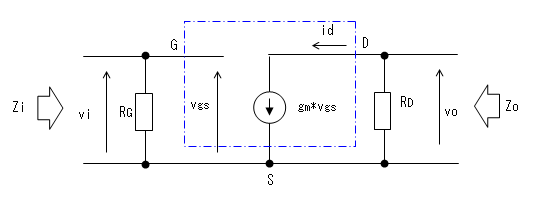

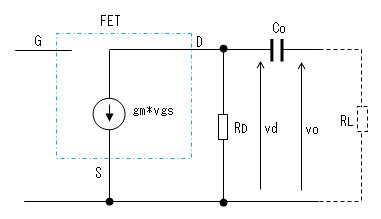

- 増幅回路の等価回路 交流の等価回路ではカップリング・コンデンサのCi、Coとバイパス・コンデンサのCSは

- 入力インピーダンスの計算 等価回路から入力インピーダンス(Zi)は

- 出力インピーダンスの計算 等価回路から出力インピーダンス(Zo)は

- 電圧増幅度の計算 増幅回路の電圧増幅度をAvとすれば次の式で与えられます。

- コンデンサーの容量の決定

またはVPとIDSSが与えられると 自動的にRSの値も決まってしまいます。

今回使用するFETの2SK2880-Dでは、データシートより

Vp = -1.5[V](typ)、IDSS = 2.5〜6.0[mA]なので、

IDSS = 4.0[mA]として計算すると

RS ≒ 0.6 * |Vp/IDSS| = 0.6 * |-1.5/0.004| = 225[Ω]

または、データシートよりyfs = 3.0[mS](typ)であることから

RS ≒ 1.2 / yfs = 1.2 / 0.003 = 400[Ω]

今回はE-6系列の抵抗値から選んでRS=330[Ω]としました。

RD = 2 * (VDD - VDS)/ IDSS−RS = 2 * (10 - 5)/0.004 - 330 = 2170[Ω]

E-6系列の抵抗値から選んでRD=2.2[kΩ]としました。

流れないので、バイアス回路の観点からは、自由に値を選ぶことが出来ます。

うるさいことを言えば、漏れ電流の影響を受けるので、大き目に設定するときは

一応調べた方がよいかも知れません。

それよりもRGは、増幅回路としての入力インピーダンスそのものとなるので、

通常大きい方がウレシイことから、ここではRG=1[MΩ]としました。

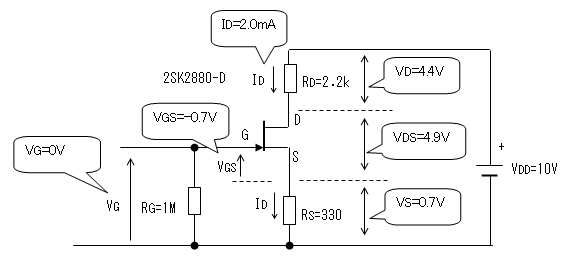

以上より決定した定数から、改めて各部の電圧を計算すると、

ID = (1/2) * IDSS = (1/2) * 0.004 = 0.002 = 2[mA]

VD = ID * RD = 0.002 * 2200 = 4.4[V]

VS = ID * RS = 0.002 * 330 ≒ 0.7[V]

VDS = VDD - VD - VS = 10.0 - 4.4 - 0.7 = 4.9[V]

短絡して考えます。増幅する周波数帯ではコンデンサのリアクタンスが十分小さく

なるように値を決めるため、交流的には短絡して考えるのですが、

その値を決めるためには、入力インピーダンスの計算が必要なので、

手順が前後するように見えますが、まず、増幅回路の等価回路から

3個のコンデンサCi、Co、CEを短絡した下図の等価回路で考えます。

FETはソース接地の 小信号簡略等価回路に置き換え、

また、VDDとグランド(GND)も交流的には同電位なので接続してあります。

Zi = RG = 1[MΩ]

となります。

Zo = RD = 2.2[kΩ]

となります。

Av = −gm * (RD // RL)

今回は、RD << RL

に設定しているので、この式は

Av = −gm * RD

となります。また、gmの値は

gm ≒ 0.7 * yfs

の式から計算します。そうすると、

gm ≒ 0.7 * 3[mS] = 2.1[mS]

Av = −2.1[mS] * 2.2[kΩ] = 4.62

となり、意外と小さいです。(^^;

-

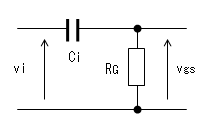

(1)入力側カップリング・コンデンサ(Ci)

Ciは入力側の抵抗RGとローカット・フィルターを形成するので

カット・オフ周波数(fi)は次の式で与えられます。

fi = 1/(2π * Ci * RG)

信号の最低周波数をfslとすれば

fsl >> fi

となるようにCiを決定すればよいことになります。よって

fsl >> 1/(2π * Ci * RG)

∴Ci >> 1/(2π * fsl * RG)

入力信号の最低周波数(fsl)を50[Hz]とします。

Ci >> 1/(2π * 50 * 1[MΩ]) ≒ 0.0032[μF]

となりかなり小さな値ですみます。今回はCi = 1[μF]としました。

(2)出力側カップリング・コンデンサ(Co)

ドレイン抵抗(RD)、負荷抵抗(RL)、 出力側カップリング・コンデンサ(Co)により

ローカット・フィルターを形成し、そのカット・オフ周波数は

次の式で与えられます。

fo = 1/{2π * Co * (RD + RL)}

信号の最低周波数をfslとすれば

fsl >> fo

となるようにCoを決定すればよいことになります。よって

fsl >> 1/(2π * Co * RG)

∴Co >> 1/{2π * fsl * (RD + RL)}

入力信号の最低周波数(fsl)を50[Hz]とします。

Co >> 1/{2π * 50 * (2.2[kΩ] + 1[MΩ])} ≒ 0.0032[μF]

となりかなり小さな値ですみます。

今回は手持ちのコンデンサーの関係でCo = 22[μF]としました。

(3)ソース・バイパス・コンデンサ(Cs)

交流的にソース抵抗Rsの影響がないように、バイパス・コンデンサCsの

定数を決定します。

FETのgmとCsはローカット・フィルター(Low Cut Filer)を構成するため

Csの値が小さいと増幅する周波数帯域の低域側で増幅度が

低下してしまいます。この影響をなくすためには、

フィルタのカットオフ周波数が信号の最低周波数より

十分小さくなるようにCsを決定します。

このローカット・フィルターのカットオフ周波数fsは、

fs = gm/(2π * CS)

となりますので、信号の最低周波数をfslとすれば

fsl >> fs

となるようにCsを決定すればよいことになります。よって

fsl >> fs = gm /[π * CE]

∴CS >> gm /(2π * fsl)

入力信号の最低周波数を(fsl)50[Hz]とします。

gmは2.1[mS]としましので

CS >> 0.0021 /[2π * 50] ≒ 6.7[μF]

となります。

電解コンデンサは経年変化により静電容量が減少しますので、

少なくとも計算値の2倍は欲しいところです。

余裕を持って、本実験では、CS = 47[μF]としました。

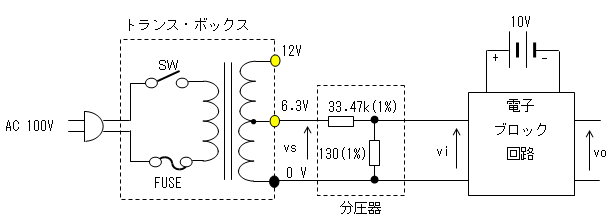

実験方法

-

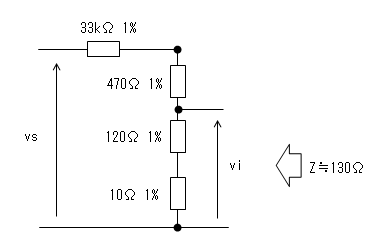

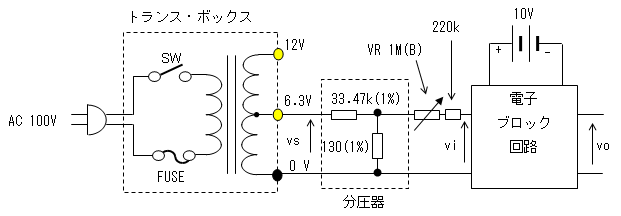

信号源としては、トランス・ボックス

を使用します。

従って、周波数は(東日本では)50Hzになります。

トランス・ボックスの出力電圧がそのままでは電圧が高過ぎるので

分圧器により分圧し、24mV(rms)程度まで減衰させます。

このとき、増幅器からみたときの信号源のインピーダンスは130Ω程度となり

FET増幅回路の入力インピーダンスZiに比べると十分小さい値となります。

- 電子ブロックの配置

- 直流動作点の測定

ディジタルテスターの直流電圧測定レンジで、下図に示すように VD、VDS、VS、

VG、GSを測定します。 IDはVDとRDの値から ID=VD/RDの式により求めます。

また、電源電圧VDDも正確に10.0[V]ではないので、測定しておきます。

- 電圧増幅度の測定

増幅回路における電圧増幅度の簡易測定法によります。

(1)下図の測定回路を組立てます。

(2)viの値を読みます。

または、vsの値を読み取り、分圧器による分圧比をかけて、viとします。

分圧比は今回の回路では、は130/33600となります。

(3)voの値を読みます。

(5)viの値とvoの値から電圧増幅度Av=vo/viを求めます。

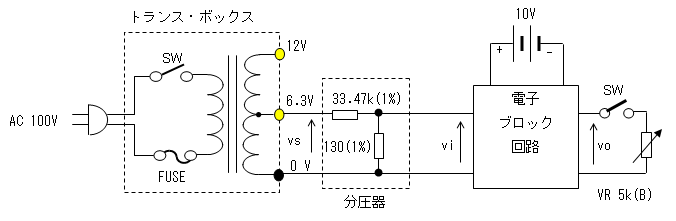

- 入力インピーダンスの測定

増幅回路における入力インピーダンスの簡易測定法によります。

(1)下図の測定回路を組立てます。

(2)VRを0[Ω]の状態にしてvoの値を読み取ります。

この時のvoの読みをvo0とします。

(3)voの値が1/2*vo0となるようにVRを調整します。

(4)VRを回路から外し、テスターの抵抗レンジでVRの値を読み取ります。

この時のVRの値がZiとなります。

- 出力インピーダンスの測定

増幅回路における出力インピーダンスの簡易測定法によります。

(1)下図の測定回路を組立てます。

(2)SWを開放の状態にしてvoの値を読み取ります。

この時のvoの読みをvo0とします。

(3)SWを閉じて(短絡)からvoの値が1/2*vo0となるようにVRを調整します。

(4)VRを回路から外し、テスターの抵抗レンジでVRの値を読み取ります。

この時のVRの値がZoとなります。

なお、SWについては、実際は配線を取り外すことにより解放しました。

実験機材

- 自作電子ブロック

-

使用したブロックは、実験方法の

電子ブロックの配置を参照。

- 簡易安定化電源 (10[V]端子)

- ディジタル・テスター

- トランス・ボックス

- 分圧器

- 可変抵抗器(5kΩB)

- 可変抵抗器(1MΩB)

- 固定抵抗器(220kΩ)

実験結果

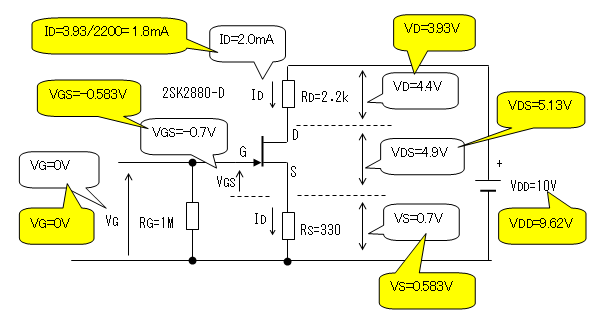

- 直流動作点の測定

下図に測定結果を示します。

白色の吹き出しで計算値、黄色の吹き出しで測定値を表しました。

VGはなるべく抵抗の近くで図ります。グランドの位置が悪いと、

実験回路の共通インピーダンス(別途記述予定)により若干の電圧が

発生することがあります。

- 電圧増幅度の測定

viの値はディジタル・テスターで直接測定しました。

viの値 [mV] voの値 [mV] 備考 24 151

以上の測定結果より、電圧増幅度Avを計算すると、

Av = vo/vi = 151/24

∴Av = 6.3

Av(絶対値)の設計値と測定値を比較すると、

Av (設計値) Av (測定値) 測定値/設計値 (%) 備考 4.62 6.3 36

- 入力インピーダンスの測定

VRの値 [kΩ] voの値 [mV] 備考 0 151 voのこの値がvo0 972 75 (vo=1/2 * vo0)

以上の測定結果より、

Zi = 972[kΩ]

Ziの設計値と測定値を比較すると、

Zi (計算値) [kΩ] Zi (測定値) [kΩ] 測定値/設計値 (%) 備考 1000 972 -2.8

- 出力インピーダンスの測定

VRの値 [kΩ] voの値 m[V] 備考 ∞ (SW:開放) 151 voのこの値がvo0 2.17 (SW:短絡) 75 (vo=1/2 * vo0)

以上の測定結果より、

Zo = 2.17[kΩ]

Zoの設計値と測定値を比較すると、

Zo (設計値) [kΩ] Zo (測定値) [kΩ] 測定値/設計値 (%) 備考 2.2 2.17 -1.4

考察

- 直流動作点

VDSが計算値と20%近い差が見られましたが、直流的には負帰還がかかり、

安定しているため問題ない範囲と考えます。

- 増幅度

設計値と測定値との差は36%であり、やや大きいようにも見えますが、負帰還をかけない

増幅回路では、デバイス毎のgmのバラつきも大きく、この程度の偏差は当然の範囲と

思われます。正確に増幅度を設定したい場合は負帰還をかける必要があるでしょう。

なお、本実験に用いたFETは、 静特性測定実験に使用したサンプルと同じであり

その実験結果から得たgmの値は2.73[mS]なので、この値から増幅度を計算すると

Av = −gm * RD = −2.73[mS] * 2.2[kΩ] = 6.006

となるので、本実験結果と整合しています。

- 入力インピーダンス

設計値と測定値との差は2.8%であり、固定抵抗(RGの誤差(5%)よりも小さく

設計通りの結果と考えます。

- 出力インピーダンス

設計値と測定値との差は1.4%であり、固定抵抗(RDの誤差(5%)よりも小さく

設計通りの結果と考えます。

今後の課題

- 周波数特性の測定

周波数特性は増幅回路の基本的な特性のひとつですが、今回の実験では

信号源として発振器ではなく、トランス・ボックスを使用する方針としたので

周波数特性の測定は断念しました。

- ひずみ率の測定

用途によってはひずみ率も重要な特性ですが、ひずみ率計が手元にないため

将来の課題としました。

参考文献

- 簡明電子回路入門(1993 第8刷) 第8章FET、矢部初男著、槇書店

- 2SK2880データシート

関連項目

- 電子回路−接合型FET

- FET増幅回路の設計− 自己バイアス回路の設計

- 電子回路− 接合型FETのソース接地増幅回路(交流負帰還なし)

- 自作計測回路−電圧増幅度の簡易測定法

- 自作計測回路−入力インピーダンスの簡易測定法

- 自作計測回路−出力インピーダンスの簡易測定法

- 自作電子ブロック

- 簡易安定化電源 (10[V]端子)

- トランス・ボックス

- 分圧器

- 可変抵抗器(5kΩB)

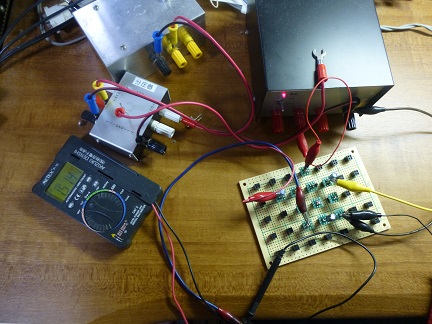

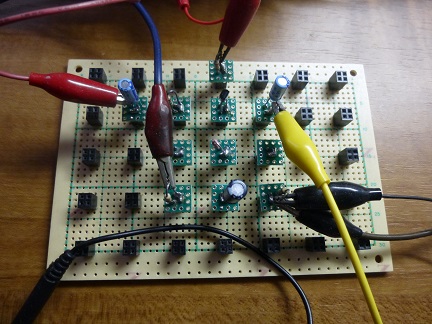

おまけ(実験中の様子)

- 実験装置全体

- 電子ブロック