実験の目的

接合型FETの動作を確認するとともに、小信号等価回路の

パラメータについて考察します。

実験課題

求めます。

-

(1)VGS-ID特性

(2)VDS-ID特性

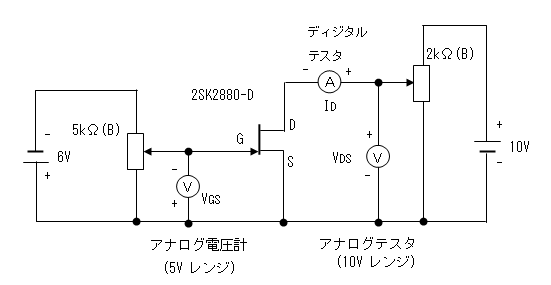

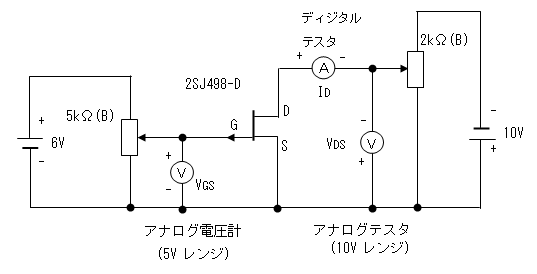

測定するデバイスは、N-チャネルタイプの2SK2880-Dと、

Pチャネルタイプの2SJ498-Dを用いて実施します。

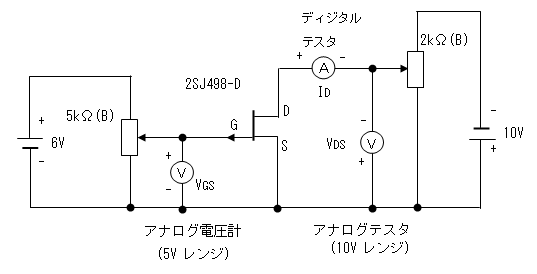

実験回路

- 2SK2880-D

- 2SJ498-D

FETの静特性

表されます。

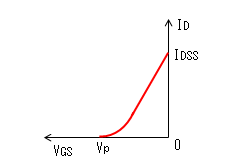

- VGS-ID特性 伝達特性であるVGS-ID特性は、次の式で近似されます。

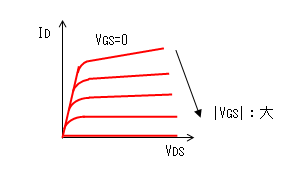

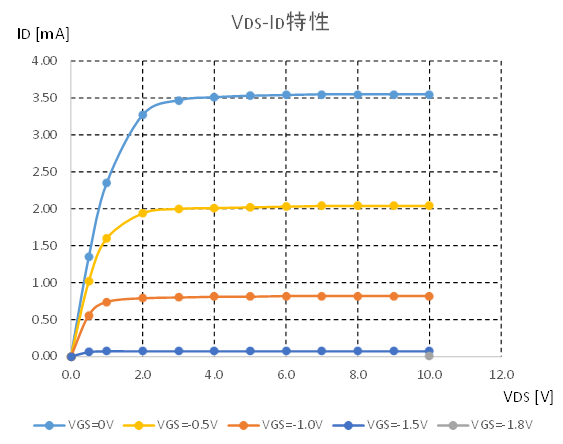

- VDS-ID特性 飽和領域(VDS>Vp)の場合、伝達特性によりIDは

ID = IDSS ( 1 - |VGS/Vp|)2

よって、IDSSとVpを通る2次関数となります。

ほぼVGSにより決定されます。

よってIDはVDSには依存せず、VGSが一定ならば、

IDもほぼ一定となるので、グラフ上は、VGSをパラメータとした

ほぼ水平なグラフとなります。

しかし、実際にはVGSが0に近い程、やや右肩上がりのグラフとなります。

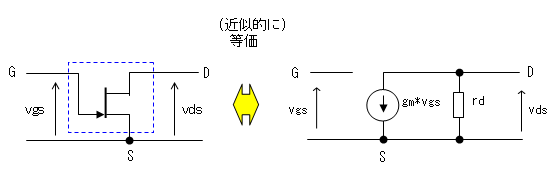

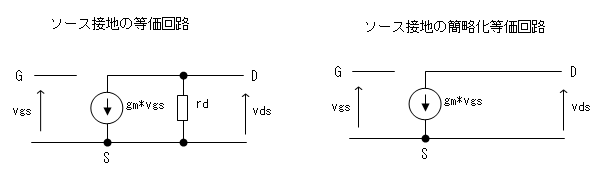

FETの小信号簡易化等価回路

回路の解析が難しいので、まずバイアスをかけて動作点を決め、

次に、小信号動作であることを前提としてその動作点においては

線形動作をするものとして近似し解析します。

線形動作をするFETは等価回路で置き換えます。

FETのソース接地における等価回路は下図です。

等価回路の中のパラメータである、gm、rdは静特性のグラフから

以下のようにして求めます。

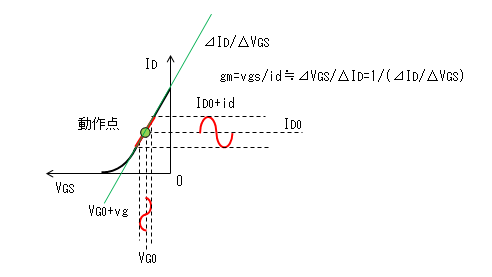

(1)gm

相互コンダクタンス(gm)は ゲート電圧の変化に対するドレイン電流の変化で

定義されるため、VGS-ID特性(伝達特性)のグラフの

動作点における接線の傾きから求められます。

VGS-ID特性は2次関数

ID = IDSS ( 1 - |VGS/Vp|)2

で近似されることから、接線すなわちはgmは、動作点が変わると変化します。

一般的には動作点はIDSSの1/2付近に設定します。

そのときのgmは、データシートに記載されたID = IDSSにおける

gmを yfsとして、 gm ≒ 0.7 * yfsで概算出来ます。

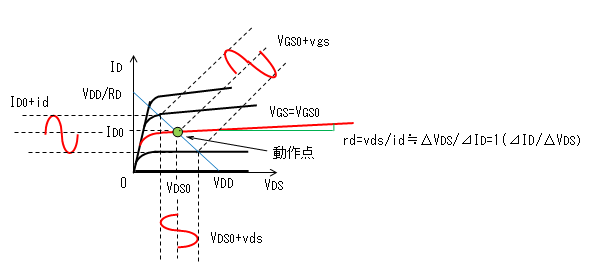

(2)rd

ドレイン抵抗(rd)は ドレイン~ソース間電圧の変化に対するドレイン電流の変化で

定義されるため、VDS-ID特性(出力特性)のグラフの

動作点における接線の傾きから求められます。

この傾きはわずかにVGSの影響を受けます。

つまりVGSが0に近い程傾きがやや大きくなります。

実験方法

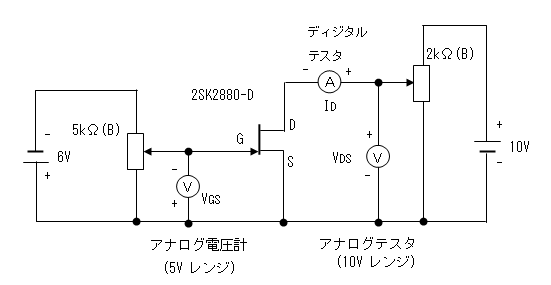

- 実験回路(再掲、2SK2880-D)

- 測定手順 VGS-ID特性とVDS-ID特性は 同時に測定します。

- 実験回路(再掲、2SJ498-D)

(1)測定回路を組立ます。電源は接続しません。

(2)回路の接続とテスターの設定をよく確認します。

(3)ふたつのVRの設定を最小に設定します。

(4)乾電池(6V)を接続し、10V電源を接続しオンにします。

(5)5kΩVRによりゲート~ソース間電圧VGSを設定します。

最初はVGS=0[V]とします。

(6)2kΩVRによりドレイン~ソース間電圧VDSを設定します。

(7)ドレイン電流IDを読み取ります。

(8)手順(6)~(7)を繰り返し、ドレイン~ソース間電圧VDSを変えながら、

ドレイン電流IDを読み取っていきます。

(9)ドレイン~ソース間電圧|VDS|を10[V]~0[V]まで変えて読み取ったら、

5kΩVRによりゲート~ソース間電圧|VGS|を増やしてから、

手順(6)~(7)を繰り返します。

(10)最後に|VDS|を最大(≒10[V])に設定し、

ゲート~ソース間電圧VGSを調整し、ドレイン電流|ID|が

10[μA]になるようにします。このときのVGSがピンチオフ電圧 VPになります。

測定データの中から、ドレイン~ソース間電圧|VDS|が10[V]のときの

ゲート~ソース間電圧VGSとドレイン電流IDとの関係を取り出すと

VGS-ID特性となります。

回路を変更して2SJ498-Dの静特性を測定します。

電源や電圧計の極性がすべて逆になるので、組み立てた回路をよく確認します。

測定手順は、2SK2880-Dと同じです。

実験機材

- FET: 2SK2880(Dランク)

- FET: 2SJ498(Dランク)

- 簡易安定化電源 (10[V]端子)

- アナログ直流電圧計 (5[V]レンジ)

- アナログ・テスター

- ディジタル・テスター

- 可変抵抗器(5kΩB)

- 可変抵抗器(2kΩB)

- 乾電池、電池ホルダー:1.5[V]×4 結果的には1.5[V]×2でも十分でしたが、データシート上Vpの最大値が

6[V]であったことから、1.5[V]×4としました。

実験結果

- 2SK2880-D

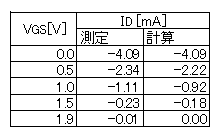

- VGS-ID特性 測定データ

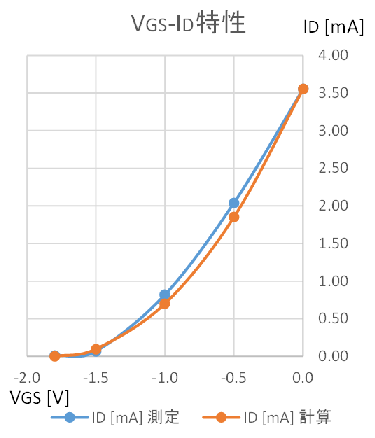

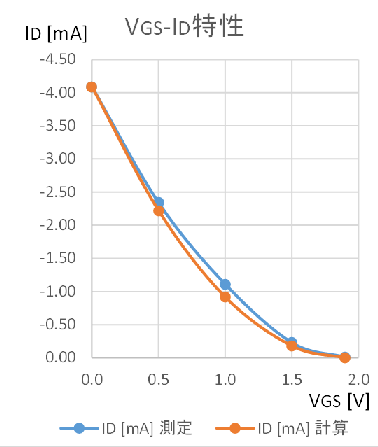

- VGS-ID特性グラフ

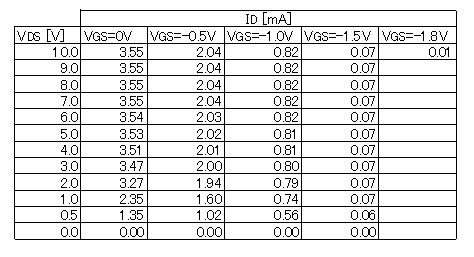

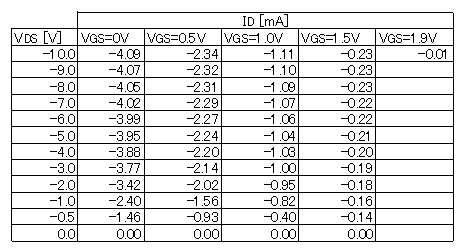

- VDS-ID特性 測定データ

- VDS-ID特性特性グラフ

- 2SJ498-D

- VGS-ID特性 測定データ

- VGS-ID特性グラフ

- VDS-ID特性 測定データ

- VDS-ID特性特性グラフ

ピンチオフ電圧(Vp)は-1.8[V]

IDSSは3.55[mA]でした。

ピンチオフ電圧(Vp)は1.9[V]

IDSSは4.09[mA]でした。

考察

- VGS-ID特性とgm 実験の結果、IDSSとVpが判りましたので、VGS-ID特性が 2次関数の

- 2SK2880-D gm = ⊿ID/⊿VGS = (3.55[mA] - 0.82[mA])/(0[V] - (-1.00[V])) = 2.73[mS]

- 2SJ498-D gm = ⊿ID/⊿VGS = (-4.09[mA] - (-1.11[mA]))/(0[V] - 1.00[V]) = 2.98[mS]

- VDS-ID特性とドレイン抵抗(rd) |VGS| = 0.5[V]を動作点と考えたときに、このグラフの直線性のよいところを選んで

- 2SK2880-D rd = ⊿VDS/⊿ID = (10[V] - 3[V])/(2.04[mA] - 2.00[mA]) = 175[kΩ]

- 2SJ498-D rd = ⊿VDS/⊿ID = (-10[V] - (-5[V]))/(-2.34[mA] - (-2.24[mA])) = 50[kΩ]

ID = IDSS ( 1 - |VGS/Vp|)2

に従うと仮定した場合を計算値としてデータの表とグラフに併記しました。

グラフを見ると、計算値は実測値より若干下回りました。

これが一般的な傾向なのかは、本実験からは判断出来ませんでした。

VGSを0.5[V]に設定したとき、IDがほぼIDSSの1/2となった

ことから、|VGS| = 0.5[V]を動作点と考え、相互コンダクタンス(gm)を 求めました。

測定点が少ないので、やや(かなり?)計算が乱暴ですが、動作点の前後の値から

下記のように計算しました。

yfsから概算したgmを下記に纏めました。

| FET型式 | データシートのグラフ から読み取ったgm |

データシートのyfs から概算式で計算したgm |

実験から求めたgm |

| 2SK2880-D | 記載なし | 2.1mS (=3(typ)*0.7) | 2.73mS |

| 2SJ498-D | 3.5mS | 2.8mS (=4(typ)*0.7) | 2.98mS |

データシートに記載されたyfsはtyp値であり、minはtypの半部以下で

あることから(maxの記載はない)、概算式の計算からgmを算出しても

実用になるものと考えます。

ドレイン抵抗を計算しました。

通常の負荷抵抗(数kΩ)より大きな値を示しているため、FETの等価回路では(rd)を

省略した簡略等価回路としても実用になるものと考えられます。

反省点

-

本実験において、測定精度が必要な物理量はIDです。

なので、精度が出るディジタル・テスターはID測定に使用しました。

最初、ID測定にはアナログ・テスターを使用したため、

変化量を読み取れず、ドレイン抵抗が計算出来ませんでした。

結果的に、ID測定にディジタル・テスターを使い、再測定するはめになりました。

今後の課題

- 測定に使用したサンプルFETを使い、増幅回路の実験を実施する。

参考文献

- 簡明電子回路入門(1993 第8刷) 第8章FET、矢部初男著、槇書店

関連項目

- 電子回路-接合型FET

- 簡易安定化電源 (10[V]端子)

- アナログ直流電圧計 (5[V]レンジ)

- 可変抵抗器(5kΩB)

- 可変抵抗器(2kΩB)