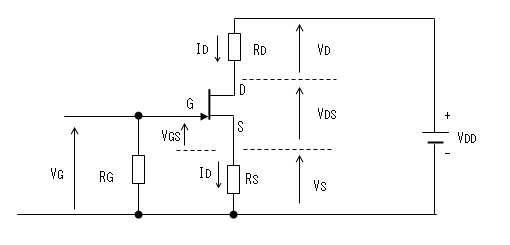

固定バイアス回路

自己バイアス回路の設計

- 自己バイアス回路の構成

- 前提条件

-

(1)電源電圧: VDD

(2)ドレイン電流(VGS = 0): IDSS

(3)ピンチオフ電圧: VP

(4)相互コンダクタンス(VGS = 0): yfs

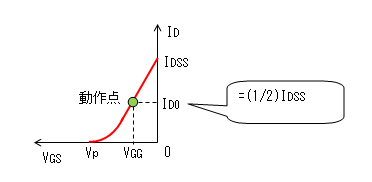

(5)FETの動作点におけるIDは(1/2)IDSSに設定する。

(6)FETのドレイン〜ソース間電圧はVDSに設定する。

(しばしば、VDSはVDDの1/2〜(VDD-Vs)の1/2あたりに

設定しましす。) (2024/5/18追記)

- バイアス回路の設計手順

-

(1)RSの計算

-

自己バイアス回路の構成から次の式が成り立ちます。

VS = RS * ID

FETのゲート(G)は抵抗器(RG)によりグランドに接続されているので

VG = 0[V]

です。従って、FETのバイアス電圧VGSは

VS + VGS = 0

∴ VGS = −VS

∴ VGS = −RS * ID ・・・・・ (1)

一方、FETの伝達特性は次の2次式で近似できます。

ID = IDSS ( 1 - |VGS/Vp|)2 ・・・・・ (2)

条件(5)より、FETの動作点としてIDを(1/2)IDSSに設定するとすれば

ID = (1/2)IDSS ・・・・・ (3)

(3)式を(1)式と(2)式にそれぞれ代入してIDを消去します。

VGS = −RS * (1/2)IDSS ・・・・・ (4)

(1/2)IDSS = IDSS ( 1 - |VGS/Vp|)2

∴ 1/2 = ( 1 - |VGS/Vp|)2 ・・・・・ (5)

(4)式を(5)式に代入してVGSを消去し、式を変形すると

1/2 = ( 1 - |−RS * (1/2)IDSS/Vp|)2

1/√2 = 1 - |−RS * (1/2)IDSS/Vp|

1/√2 = 1 - RS * |(1/2)IDSS/Vp|

RS * |(1/2)IDSS/Vp| = 1 - 1/√2

RS = (1 - 1/√2) * |2 * Vp/IDSS|

RS = (1 - 1/√2) * 2 * |Vp/IDSS|

∴ RS ≒ 0.6 * |Vp/IDSS| ・・・・・ (6)

を得ます。また、

yfs = 2 * |IDSS/Vp|

の関係があるので、これを(6)式に代入すると

RS ≒ 0.6 * (2 / yfs)

∴ RS ≒ 1.2 / yfs ・・・・・ (7)

と表すことも出来ます。

これら、Vp、IDSS、yfsなどはいずれもFETのデータシートで 与えられています。

ただし、(2)式が近似式であることや、Vp、IDSS、yfsに バラツキがあることなどから

(データシートの記載値はtyp値)、(6)式での計算値と(7)式での計算値は

多少異なることが多いです。

-

自己バイアス回路の構成から

VDD - VDS = ID * (RD + RS)

これに(3)式を代入すると

RD = 2 * (VDD - VDS)/ IDSS−RS

を得ます。

-

RGはゲート端子の電位を0[V]に決める働きがありますが、

電流は流れないので、バイアス回路の観点からは任意に決められます。

ただし、RGは交流的には入力インピーダンスに影響します。

また、ドレイン(D)からゲート(G)に向けてわずかにもれ電流があるので

極端に大きな値にしてしまうと、直流的にも影響が出る可能性があります。

(もれ電流の最大値はデータシートに記載があります。)

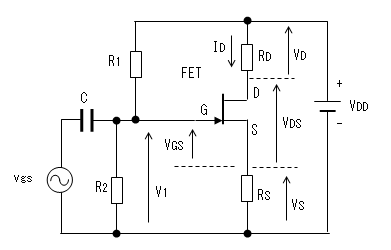

自己バイアス回路の応用

で決まることから、動作点を決めると自動的に決まってしまいます。

しかし実際の設計では、この値よりVsを高くしたい場合の生じることがあります。

そこで、ゲート電圧を高くするために、下図のように抵抗器R1、 R2

を接続するとゲートの直流電圧V1を0[V]から V1 = R2/(R1 + R2) * VDD

とすることで、Vs(=V1−VGS)を任意に設定出来ます。

つまりVDDをR1とR2で 分圧したことになります。

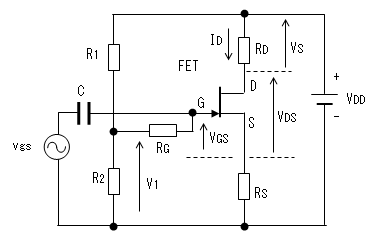

このときR1とR2により入力インピーダンスが 下がってしまう

ことを嫌う場合は、さらに下図のようにRGを追加します。

RG >> R1, R2に選定すればFETの 高入力インピーダンスを

損なわずに済みます。

FET増幅回路を設計する場合、まずFETに流すドレイン電流ID (=ソース電流)を決めた後、

増幅回路各部の電圧配分を決めると、設計し易いかと思います。

電圧配分の決定にあたっては、ゲート〜ソース間電圧VGSがいくらになるかを

知りたくなるのですが、FETのゲート電圧とドレイン電流の関係は下記の式で近似出来ます。

ID = IDSS ( 1 - |VGS/Vp|)2

IDSSとVpはFETを選定すると決まります。またIDを(1/2)*IDSS とすれば、

この式をVGSについて解くと

|VGS| = (1 - 1/√2)*|Vp|

∴ |VGS| ≒ 0.3*|Vp|

の式を得ます。

VGSが決まれば、

V1 = VGS + VS

の関係があるので、VSを決めれば、V1が決まり、

または、V1を決めれば、VSが決まります。

そうすると、

Rs = VS / ID

となります。また、

V1 = R2 / (R1 + R2) * VDD

となるように、R1とR2を決めます。

FETのゲート(G)には電流が流れないので、バイポーラ・トランジスタのように

R1とR2に大きな電流(ブリーダ電流)を流す必要はありません。

また、(VDD-VS)が(VD+VDS)となるので、 VDの配分を決めれば

RD = VD / ID

となります。

FETの1石増幅回路の設計

- ソース接地増幅回路(交流負帰還なし)

- 回路の解析 電子回路の接合型FETの ソース接地増幅回路(交流負帰還なし)を参照してください。

- 設計事例 FETのデバイス実験の ソース接地増幅回路(交流負帰還なし)などを参照してください。

- ソース接地増幅回路(交流負帰還あり)

- 回路の解析 電子回路の接合型FETの ソース接地増幅回路(交流負帰還あり)を参照してください。

- 設計事例 FETのデバイス実験の ソース接地増幅回路(交流負帰還あり)などを参照してください。

- ドレイン接地増幅回路

- 回路の解析 電子回路の接合型FETの ドレイン接地増幅回路を参照してください。

- 設計事例 FETのデバイス実験の ドレイン接地増幅回路などを参照してください。

- ゲート接地増幅回路

-

工事中です。

2段直結増幅回路(ソース接地〜ソース接地の設計)(工事中)

ほとんど(全く?)見かけません。(^^;

ネットで検索しても全くヒットしません。

おそらくメリットが全くないからだと思われます。

その理由としては◆後報◆

- 回路図

- 交流等価回路

- 入力インピーダンス

- 出力インピーダンス

- 電圧増幅度

- 入力カップリング・コンデンサーの影響

- 出力カップリング・コンデンサーの影響

2段直結増幅回路(ソース接地〜ドレイン接地)の設計(工事中)

- 回路図

- 交流等価回路

- 入力インピーダンス

- 出力インピーダンス

- 電圧増幅度

- 入力カップリング・コンデンサーの影響

- 出力カップリング・コンデンサーの影響

差動増幅回路の設計の設計(工事中)

- 回路図

- 交流等価回路

- 入力インピーダンス

- 出力インピーダンス

- 電圧増幅度

- 入力カップリング・コンデンサーの影響

- 出力カップリング・コンデンサーの影響

直流増幅回路の設計(工事中)