実験の目的

その効果を確認します。

実験課題

- スピードアップ・コンデンサーの効果を波形で確認 コンデンサーの容量を変えながら出力波形の遅延時間を測定し、

適切と思われる容量の値を検討します。

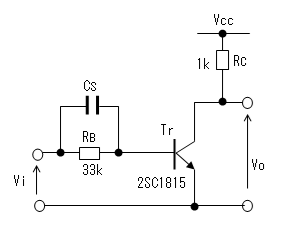

実験回路

回路の機能と動作

-

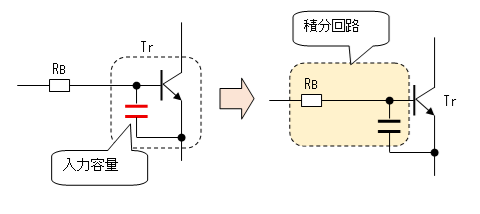

トランジスタ・スイッチをベース電圧でON/OFFさせる際、ベースが持つ容量と

ベース抵抗(RB)により積分回路が形成されるため、スイッチング速度が

遅くなります。

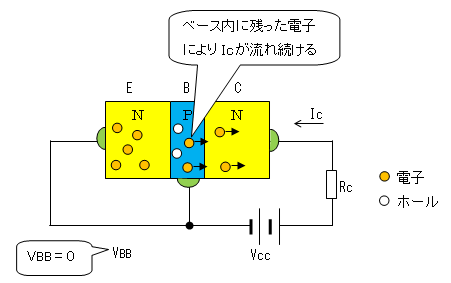

トランジスタ・スイッチがONからOFFになる際のもうひとつの遅延理由は、

ベース内の蓄積電荷です。ベース電流が0になっても蓄積電荷によりコレクタ電流が

すぐには0になりません。

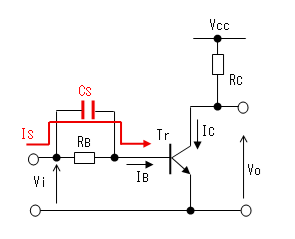

RBと並列にスピードアップ・コンデンサー(CS)を接続すると、

ベースが持つ容量が早く充放電されるため、スイッチング速度が改善されます。

また蓄積電荷も早く排出されます。

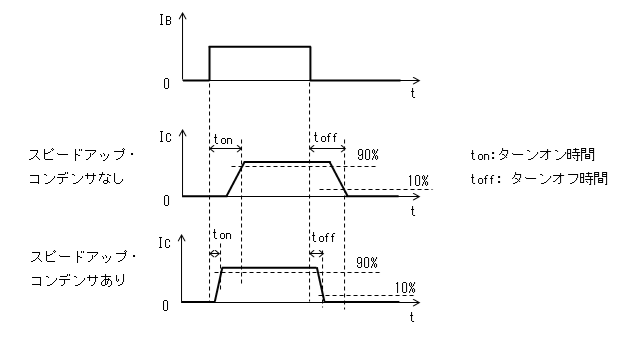

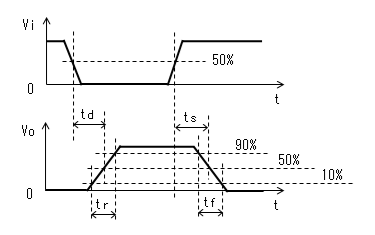

動作波形

スピードアップ・コンデンサーの機能の詳細については、トランジスタ・パルス回路の

解析に記載した スピードアップ・コンデンサーの機能を参照してください。

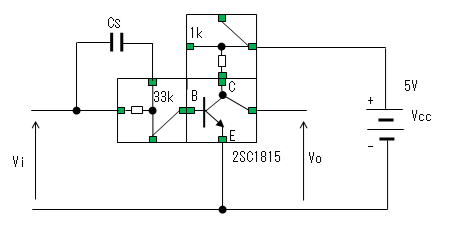

実験回路の設計

- 設計条件 (1)電源電圧:およそ5[V]とします。

- RCの選定

- RBの選定

- CSの選定

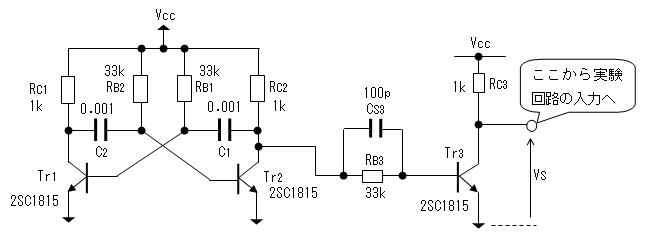

- 信号源 非安定マルチバイブレータの 実験に使用した電子ブロックを流用しました。

(2)使用するトランジスタ:定番の2SC1815-Y

(3)コレクタ電流(ON状態):5[mA]

(4)入力信号

非安定マルチバイブレータの実験 で使用した実験回路を流用します。

ただし、コンデンサーの容量は変更し発振周期は変えます。

・波形:矩形波

・周波数:約25[kHz]

・デューティー:約50[%]

・振幅:0-5[V]

(5)出力の負荷

トランジスタのコレクタには何も接続しません。

波形観測のためのオシロスコープを接続しますが、オシロの入力インピーダンスは

[MΩ]のレベルなので無視出来る値です。

-

Vcc=5[V]、コレクタ電流(IC(ON))が5[mA]なので

RC = Vcc / IC(ON) = 5[V] / 5[mA] = 1[kΩ]

-

トランジスタの直流電流増幅率(hFE)はデータシートより120(min)なので

トランジスタのベース電流は

IB = Ic / hFE(min) = 5[mA] / 120 ≒ 41.6[μA]

トランジスタがONしたとき確実に飽和するよう、通常この値の2~10倍くらいの

ベース電流が流れるようRBを決めますが、まずは3倍で計算しました。

RB = (Vcc - VBE) / IB = (5 - 0.7) / (41.6[μA] * 3) ≒ 34.5[kΩ]

E6系列より選定して RB = 33[kΩ]としました。

-

解析的に決めるのは難しく10~100[pF]の範囲で調整します。

今回は手持ちのコンデンサーにあった、10、30、47、100[pF]を選定して

波形の変化を観測しました。

ただし、発振周期とデューティを変更するために、CB1 = 0.001[μF]、 CB2 = 0.001[μF]

に変更してます。この場合の発振周期は約40[μs]、デューティーは約50[%]です。

ところで、非安定マルチバイブレータの出力を直接使うと立上がりの時間が遅く

実験回路の応答特性が正確に判りません。本来は、非安定マルチバイブレータの出力を

一度、シュミット・トリガ回路を通すと良いのですが、回路設計の負担が増えると

同時に、部品も増えてしまいます。

そこで、非安定マルチバイブレータの出力にスピードアップ・コンデンサーを

追加したトランジスタ・スイッチを経由して実験回路に供給します。

今回実験する回路を信号源に使ってしまっては、ちぐはぐな実験になってしまうのですが

妥協して諦めることにしました。(T_T;

下記が信号源全体の回路図です。

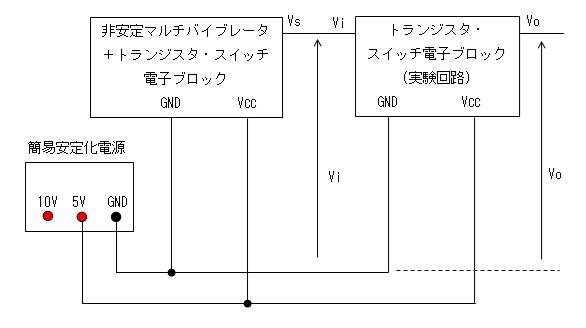

実験方法

- 電子ブロックの配置 電子ブロックで実験回路を下図のように組み立てます。

- 全体の接続図

- 波形の観測 スピードアップ・コンデンサーの値を変えながらViとVoの波形を

電源は簡易安定化電源の5[V]端子を使用しました。

オシロスコープで観測し、下図に示す td、ts、tr、tfを読み取ります。

実験機材

実験結果

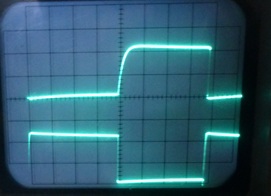

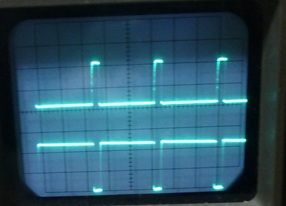

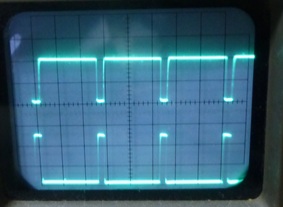

- 信号源の波形 上が非安定マルチバイブレータの波形、下は100[pF]のスピードアップ・コンデンサーを

- 波形観測(遅延時間測定) td、ts、tr、tfの読み取り結果を下記に 示します。

を付加したトランジスタ・スイッチの波形(Vs)。

Vsのtrは100[ns]、tfは80[ns]くらいでしたが、多少、

次段に接続される実験回路のCSの影響を受けるようです。

2V/div、5μs/div

波形の写真は面倒なので省略しました。

(似たような波形ばかりで楽しくないので。笑)

| CSの容量 [pF] |

td[ns] | ts[ns] | tr[ns] | tf[ns] | 備考 |

| 0 | 1800 | 200 | 700 | 160 | スピードアップ・ コンデンサー(CS)なし |

| 10 | 1500 | 40 | 600 | 80 | |

| 30 | 500 | ≒0 | 600 | 20 | |

| 47 | 40 | ≒0 | 80 | ≒0 | |

| 100 | ≒0 | ≒0 | 80 | ≒0 |

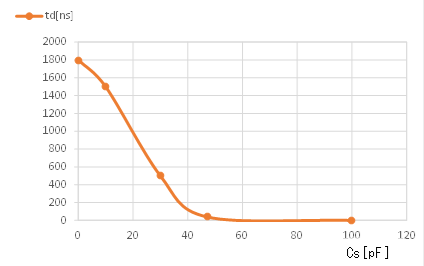

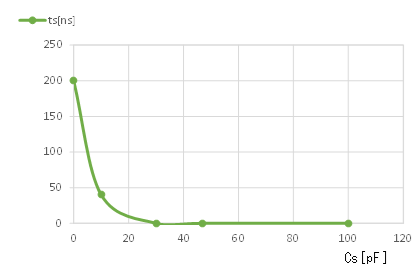

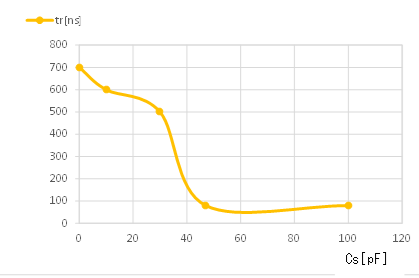

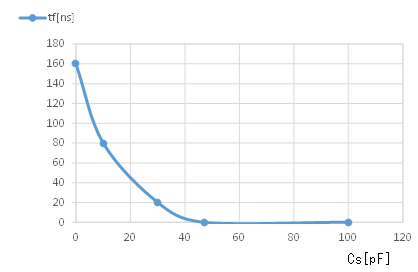

読み取った結果をグラフにしたものが下記です。

(1)td

(2)ts

(3)tr

このグラフだけなぜか歪んでしましいました。比較的ラフに値を読み取ったことと

オシロスコープのレンジの切替わりだったせいかもしれません。(-_-?

(4)tf

測定結果・考察

- 遅延時間の改善 想像していたよりも絶大な(?)効果があることが判りました。(・o・;;

- スピードアップ・コンデンサーの値 td、ts、tr、tfのいずれにおいても 47[pF]以上あれば十分な改善が期待できることが判りました。

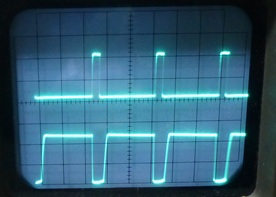

- 追加実験 信号源である非安定マルチバイブレータのコンデンサー(CB1、CB2)の

とくにスピードアップ・コンデンサーがない場合、tdとts の差が大きく、

高速なパルスを入力した場合、出力のデューティーが大きく変化して

しまうことが判りました。(追加実験の項、参照)

ただしこの値は条件(トランジスタの型式や電源電圧、ON時の入力電流など)

によって変わる可能性があり、今回の実験だけでは一般論とは言えないです。

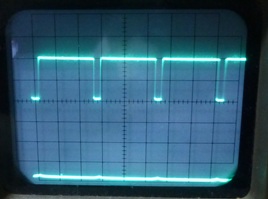

片方を100[pF]とし、非対称な矩形波をViとして入力した場合のVoの波形を

観測しました。

| デューティー | スピードアップ・ コンデンサー:47[pF] |

スピードアップ・ コンデンサー:なし |

備考 |

| 10% |  ほぼVoはViを反転した波形。 |

パルス幅が約2倍に広がった。 |

|

| 90% |  ほぼVoはViを反転した波形。 |

パルスが消えてしまった。 |

下:Vo、2V/div、5μs/div

今後の課題

- スピードアップ・コンデンサーの応用検討 将来的に、トランジスタを使用したパルス発生器の製作に応用予定です。

参考文献

- パルス回路の設計(昭和56年(1981) 第20版(改訂10版)) P-34~37 トランジスタのスイッチ動作、猪飼國夫著、CQ出版社

関連項目

- トランジスタ・パルス回路の解析- スピードアップ・コンデンサーの機能

- トランジスタ・パルス回路の実験- 非安定マルチバイブレータの実験

- 自作電子ブロック

- 簡易安定化電源