嶲峫暥專

| No. | 婰帠 | 弌斉幮 | 挊幰 | 巇條 | 夞楬婯柾 | 摿挜 | 旛峫 | |

| 僨乕僞 僶僗暆 | 柦椷傾僪儗僗嬻娫 | |||||||

| 1 | CPU偺憂傝偐偨(2003) | 枅擔僐儈儏僯働乕僔儑儞 | 搉攇堣 | 4 bit | 8bit亊16儚乕僪 | TTL 10屄 | 媶嬌偺嵟彫巇條CPU | 丂 |

| 2 | 嶨帍 僾儘僙僢僒 4價僢僩CPU(1986) | 媄弍昡榑幮 | 惎栰桽 | 4 bit | 4bit亊4k儚乕僪 | TTL 96屄 | 丂 | 丂 |

| 3 | 僩儔儞僕僗僞媄弍 SPECIAL No.48 嶌傟偽夝傞CPU(1994) | CQ弌斉幮 | 懞揷榓怣 | 8 bit | 64k僶僀僩 | TTL 栺60屄 | 儅僀僋儘僾儘僌儔儉 曽幃 ALU偼EP-ROM 偱幚尰 | 丂 |

| 4 | Verilog-HDL偵傛傞 僩僢僾僟僂儞愝寁 (1994) | CQ弌斉幮 | E.Sternheim 懠4柤挊 堜忋丄楅栘栿 | 32 bit | 4G僶僀僩? | HDL偵傛傞婰弎偺傒 | 丂 | 徻嵶偼枹撉 |

| 5 | 嶨帍丂楢嵹 僩儔儞僕僗僞媄弍 ASIC偱嶌傞 儅僀僋儘僾儘僙僢僒 (1988 Feb.乣1989 Jan.) | CQ弌斉幮 | 撿廆岹 | 16 bit | 16bit亊64k儚乕僪 | 愝寁偺傒 | COMET巇條 | 丂 |

| 6 | HDL偵傛傞 崅惈擻僨傿僕僞儖 夞楬愝寁(2002) | CQ弌斉幮 | 怷壀悷晇 | 8 bit | 14bit亊1k儚乕僪 | FLEX 10K 栺700僙儖 | PIC16F84 僒僽僙僢僩 | 丂 |

| 7 | 嶨帍 Design Wave Magazin 摿廤 巹偼偙偆偟偰CPU傪 奐敪偟偨 (1999 Nov.) | CQ弌斉幮 | 孖恵婎峅 | 16 bit | 昗弨64k僶僀僩 嵟戝4G僶僀僩 | HDL偵傛傞僐傾 | 丂 | 徻嵶偼枹撉(^^; |

| 8 | 嶨帍 Design Wave Magazin丂楢嵹 僐儞僷僋僩側16價僢僩 CPU傪愝寁偡傞 (2003 Jul.乣 ) | CQ弌斉幮 | 惔悈彯旻 斞揷壚梞 | 亂挷嵏拞亃 | 亂挷嵏拞亃 | 丂 | PDP-11 屳姺柦椷 | 徻嵶偼枹撉 |

| 9 | 嶌偭偰妛傇CPU 愝寁擖栧(2007) | 嫟棫弌斉 | 梩嶳惔婸 | 8 bit | 32byte | FLEX 10K10 | 僆儕僕僫儖 8柦椷 | 丂 |

| 10 | HDL偵傛傞 VLSI愝寁 戞2斉(2002) | 嫟棫弌斉 | 怺嶳惓岾 杒懁復晇 廐揷弮堦 楅栘惓殸 | 8 bit | 32偺kbyte | 丂 | 僆儕僕僫儖 16bit挿 | 丂 |

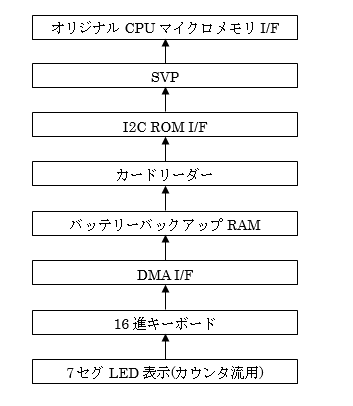

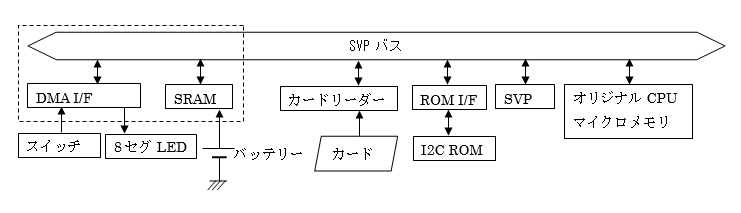

SVP(Service Processor)亂TTL斉亃

- SVP偺栚揑 儅僀僋儘僾儘僌儔儉曽幃傪憐掕偟偰偄傞CPU偺1崋婡丄2崋婡偵偮偄偰丄

- 奐敪儘乕僪儅僢僾

- SVP偺僽儘僢僋恾(巄掕斉)

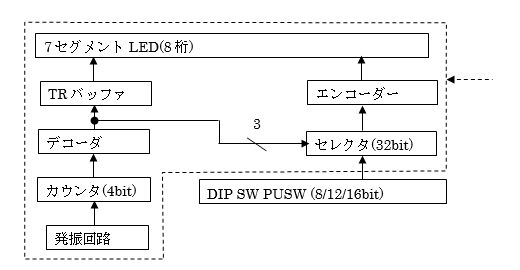

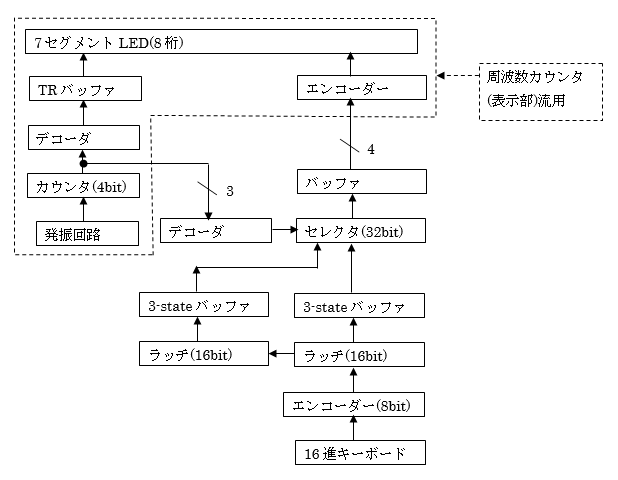

- 7僙僌LED昞帵婍 廃攇悢僇僂儞僞偺幚尡儌僕儏乕儖傪棳梡梊掕丅

- 16恑僉乕儃乕僪

- DMA I/F

- 僶僢僥儕乕僶僢僋傾僢僾RAM

- 僇乕僪儕乕僟乕I/F 庤彂偒儅乕僋僔乕僩偺SVP僾儘僌儔儉傪僼僅僩儕僼儗僋僞傪巊偭偰撉傒崬傒

- I2C ROM I/F

- SVP

- 儅僀僋儘儊儌儕I/F

儅僀僋儘僾儘僌儔儉偺奐敪丄儘乕僨傿儞僌傪巟墖偡傞憰抲偱偡丅

僶僢僥儕乕僶僢僋傾僢僾SRAM偵帺摦揮憲偟傑偡丅

1崋婡(TTL-FPGA屳姺婡)亂FPGA斉亃

- 奐敪曽恓

- 屻擔丄TTL偺傒偱幚尰偡傞偙偲傪憐掕偟偨榑棟偲偡傞丅

- 儅僀僋儘丒僾儘僌儔儉惂屼曽幃

- 壖憐婡夿傪幚尰偡傞偙偲傪憐掕偟偨傾乕僉僥僋僠儍丅

- 僋儘僗丒僐儞僷僀儔丄僋儘僗丒傾僙儞僽儔偼巊梡偟側偄丅

- 巇條

- 儅僀僋儘丒僾儘僌儔儉(1僶儞僋偁偨傝)

- 柦椷挿: 16價僢僩

- 儊儌儕嬻娫:4k儚乕僪

- 僔僗僥儉丒僶僗偐傜彂偒姺偊壜擻

- 儗僕僗僞

- 僨乕僞暆:8價僢僩

- 儗僕僗僞悢:16杮

- 俙俴倀

- 僨乕僞暆:8bit

- 墘嶼婡擻:8捠傝

- 僼儔僌

- 僨傿僗僋儕乕僩峔惉

-

(1)C僼儔僌

(2)Z僼儔僌

(3)N僼儔僌

- 僽儘僢僋恾

- 惂屼晹僽儘僢僋恾

- 僨乕僞晹僽儘僢僋恾

- 僽儘僢僋暿婡擻

- 僾儘僌儔儉ROM

杮CPU偵傛傝幚峴偝傟傞柦椷岅(僾儘僌儔儉)偑奿擺偝傟傞丅

柦椷挿偼1儚乕僪偁偨傝丄12價僢僩偱偁傞丅

柦椷偑奿擺偝傟傞ROM偵偼儚乕僪枅偵8價僢僩偺傾僪儗僗偑妱晅傜偰偍傝丄

僾儘僌儔儉僇僂儞僞(PC)偵傛傝巜掕偝傟偨傾僪儗僗偵奿擺偝傟偨柦椷岅偑

儚乕僪扨埵偱撉傒弌偝傟傞丅

僾儘僌儔儉偺曄峏偼HDL偺彂偒姺偊偲FPGA偺嵞崌惉偵傛傝峴偆丅

- 僾儘僌儔儉丒僇僂儞僞(PC)

幚峴偡傞柦椷偑奿擺偝傟偨僾儘僌儔儉ROM偺傾僪儗僗傪巜掕偡傞偨傔偺億僀儞僞偱偁傞丅

PC偼8價僢僩挿偱偁傞丅廬偭偰丄嵟戝28 = 256儚乕僪偺ROM傪巜掕弌棃傞丅

捠忢丄柦椷偼傾僪儗僗弴偵幚峴偝傟傞偨傔丄PC偼傂偲偮偺柦椷傪幚峴偡傞搙枅偵

僀儞僋儕儊儞僩偝傟傞偑丄暘婒柦椷偑幚峴偝傟偨偲偒偼丄柦椷岅撪偱巜掕偝傟偨傾僪儗僗偵

暘婒偡傞丅偡側傢偪丄暘婒偡傞傾僪儗僗偺抣偑僾儘僌儔儉丒僇僂儞僞偵奿擺偝傟傞丅

儕僙僢僩帪偼丄PC偼0僋儕傾偝傟傞丅廬偭偰丄儕僙僢僩屻偵嵟弶偵幚峴偝傟傞柦椷偼

僾儘僌儔儉ROM偺0斣抧偐傜奿擺偝傟偰偄側偗傟偽側傜側偄丅

- W儗僕僗僞

傾僉儏乕儉儗乕僞偲傕屇偽傟傞丅墘嶼傪峴偆偲偒偵拞怱偲側傞儗僕僗僞偱偁傝丄

2崁墘嶼傪峴偆偲偒偼丄昁偢墘嶼僨乕僞偺堦曽偼W儗僕僗僞偵側偗傟偽側傜側偄丅

- 斈梡儗僕僗僞

張棟偡傞僨乕僞傗惂屼忣曬傪奿擺偡傞儗僕僗僞偱偁傝丄幚峴偝傟傞柦椷岅偵傛傝

巊梡偡傞儗僕僗僞偑巜掕偝傟傞丅

- ALU

僨乕僞偵懳偟偰墘嶼張棟傪偡傞儐僯僢僩偱偁傝丄幚峴偝傟傞柦椷岅偵傛傝巜掕偝傟偨

儗僕僗僞傛傝憲傜傟偰偒偨僨乕僞偵懳偟偰丄柦椷岅偱巜掕偝傟偨墘嶼傪幚峴偡傞丅

幚峴寢壥偵懳偡傞僼儔僌偺抣傕惗惉偡傞丅

- 僼儔僌

ALU偺幚峴寢壥偵傛傝C僼儔僌丄Z僼儔僌丄N僼儔僌偺抣傪曐帩偡傞丅

峏怴偝傟傞僼儔僌偼柦椷偵傛傝堎側傞丅

僼儔僌偼忦審晅暘婒柦椷偺暘婒忦審傗丄僼儔僌傪嶲徠偡傞柦椷偱巊梡偝傟傞丅

- DO儗僕僗僞

杮僾儘僙僢僒偺奜傊弌椡偡傞僨乕僞傪奿擺偡傞丅

- DI儗僕僗僞

杮僾儘僙僢僒偺奜偐傜庢傝崬傓僨乕僞偑奿擺偝傟傞丅

- 俙俴倀徻嵶巇條

- 8價僢僩

- 柦椷

- 僼儔僌:C僼儔僌丄Z僼儔僌丄N僼儔僌

- C僼儔僌: 壓婰偺忦審偱僙僢僩偝傟傞丅柦椷偛偲偺摦嶌偼柦椷昞嶲徠偺偙偲丅

(1)壛嶼柦椷(add, adc)幚峴帪僉儍儕乕(Carry)偑敪惗偟偨応崌丅

(2)儘乕僥乕僩柦椷

(3)僔僼僩柦椷 - Z僼儔僌: 墘嶼寢壥偑0偱偁傞応崌僙僢僩偝傟傞丅

- N僼儔僌: 墘嶼寢壥偑晧偱偁傞応崌丄偡側傢偪儗僕僗僞偺MSB=1偱偁傞応崌僙僢僩偝傟傞丅

- 儅僀僋儘柦椷宍幃

- 僕儍儞僾柦椷

- 懄抣壛嶼柦椷

- 墘嶼柦椷

- COND丂(僕儍儞僾忦審)

- REG丂(儗僕僗僞巜掕)

- FUNC2丂(墘嶼巜掕)丂(僼儔僌佀 仜:曄壔偡傞丄亅:曄壔偟側偄)

- d丂(墘嶼寢壥偺奿擺愭)

- 僔僗僥儉丒僶僗

- 僗儘僢僩峔惉(埬)

- H8儅僀僐儞偲屳姺惈偺偁傞僶僗

- 僨乕僞暆:8bit

- 傾僪儗僗嬻娫:1M僶僀僩(20bit) 偨偩偟丄僆儕僕僫儖CPU偲偟偰偼64k僶僀僩(16bit)

- 儊儌儕丒儅僢僾僪I/O

- 怣崋慄堦棗

- 俬俹俴

- 俢俵俙僀儞僞僼僃乕僗

- 婡擻

- 幚憰僀儊乕僕

- 徻嵶愝寁

- 僥僗僩夞楬偲僥僗僩丒僾儘僌儔儉

- 僨乕僞揮憲(擖弌椡丄懄抣)

- ALU僥僗僩(1寘揹戩)

- 7segment LED僟僀僫儈僢僋昞帵

- 僨傿僕僞儖帪寁

- LCD昞帵

- 僔儕傾儖丒僷儔儗儖曄姺

- 僉乕儃乕僪擖椡(僠儍僞儕儞僌彍嫀)

- 僷儔儗儖丒僔儕傾儖曄姺

- 僗僥僢僺儞僌丒儌乕僞懍搙惂屼

- DC儌乕僞懍搙惂屼(PWM)

- D/A曄姺

- A/D曄姺(捈棳揹埑寁)

- 壖憐婡夿偺幚尰僾儘僌儔儉

| 抣 | 僯乕儌僯僢僋 | 婡擻 |

| 000 | add | 壛嶼(Cy柍) |

| 001 | adc | 壛嶼(Cy晅) |

| 010 | and | 價僢僩枅偺榑棟愊 |

| 011 | or | 價僢僩枅偺榑棟榓 |

| 100 | xor | 價僢僩枅偺攔懠揑榑棟榓 |

| 101 | rotr | 塃儘乕僥乕僩 |

| 110 | shra | 塃嶼弍僔僼僩 |

| 111 | shrl | 塃榑棟僔僼僩 |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | COND | 傾僪儗僗 | |||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 0 | d | FUNC1 | REG | IMM | ||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 1 | d | x | REG | FUNC2 | xxxxx | |||||||||

| 抣 | 僯乕儌僯僢僋 | 婡擻 |

| 000 | C | Carry價僢僩=1側傜僕儍儞僾 |

| 001 | NC | Carry價僢僩=0側傜僕儍儞僾 |

| 010 | Z | Zero價僢僩=1側傜僕儍儞僾 |

| 011 | NZ | Zero價僢僩=0側傜僕儍儞僾 |

| 100 | M | N價僢僩=1側傜僕儍儞僾 |

| 101 | P | N價僢僩=0側傜僕儍儞僾 |

| 110 | ALL | 柍忦審偵僕儍儞僾 |

| 111 | IR | IR儗僕僗僞偺抣偵僕儍儞僾亂専摙拞亃 |

| 抣 | 僯乕儌僯僢僋 | 慖戰儗僕僗僞 |

| 0000 | A | A儗僕僗僞 |

| 0001 | IR | 柦椷儗僕僗僞 |

| 0010 | CI/CO | 惂屼儗僕僗僞 |

| 0011 | DI/DO | DI/DO儗僕僗僞 |

| 0100 | GR0 | 斈梡儗僕僗僞0 |

| 0101 | GR1 | 斈梡儗僕僗僞1 |

| 0110 | GR2 | 斈梡儗僕僗僞2 |

| 0111 | GR3 | 斈梡儗僕僗僞3 |

| 1000 | BH | BH儗僕僗僞 |

| 1001 | BL | BL儗僕僗僞 |

| 1010 | RH | RH儗僕僗僞 |

| 1011 | RL | RL儗僕僗僞 |

| 1100 | SH | SH儗僕僗僞 |

| 1101 | SL | SL儗僕僗僞 |

| 1110 | PH | PH儗僕僗僞 |

| 1111 | PL | PL儗僕僗僞 |

| 抣 | 僯乕儌僯僢僋 | 婡擻 | C僼儔僌 | Z僼儔僌 | N僼儔僌 |

| 000 | add | 壛嶼(Cy晅) | 仜 | 仜 | 仜 |

| 001 | adc | 壛嶼(Cy柍) | 仜 | 仜 | 仜 |

| 010 | and | 價僢僩枅偺榑棟愊 | 亅 | 仜 | 仜 |

| 011 | or | 價僢僩枅偺榑棟榓 | 亅 | 仜 | 仜 |

| 100 | xor | 價僢僩枅偺攔懠揑榑棟榓 | 亅 | 仜 | 仜 |

| 101 | rotr | 塃儘乕僥乕僩 | 仜 | 仜 | 仜 |

| 110 | shra | 塃僔僼僩(嶼弍) | 仜 | 仜 | 仜 |

| 111 | shrl | 塃僔僼僩(榑棟) | 仜 | 仜 | 仜 |

| 抣 | 婡擻 |

| 0 | 奿擺愭偼A儗僕僗僞 |

| 1 | 奿擺愭偼REG偵傛傞巜掕儗僕僗僞 |

| 僗儘僢僩No. | 僆儕僕僫儖CPU (TTL斉) | 僆儕僕僫儖CPU (FPGA斉) | H8儅僀僐儞斉 |

| 1 | DMA僀儞僞僼僃乕僗 | DMA僀儞僞僼僃乕僗 | (梊旛) |

| 2 | SVP + I2C-ROM | FPGA CPU | H8儅僀僐儞CPU +僔儕傾儖 |

| 3 | TTL CPU | ||

| 4 | VRAM | ||

| 5 | 僉乕儃乕僪(PS2) + I/O | ||

| 6 | File僀儞僞僼僃乕僗(IDE) | ||

| 7 | LAN僀儞僞僼僃乕僗(10BaseT | ||

| 8 | 梊旛(USB丄傑偨偼奼挘僶僗 etc.) | ||

| 怣崋柤 | 杮悢 | 婡擻 | 旛峫 |

| A[19:0] | 20 | 傾僪儗僗 | 丂 |

| D[7:0] | 8 | 僨乕僞 | 丂 |

| AS_N | 1 | 傾僪儗僗丒僗僩儘乕僽 | 丂 |

| RD_N | 1 | 儕乕僪丒僗僩儘乕僽 | 丂 |

| WR_N | 1 | 儔僀僩丒僗僩儘乕僽 | 丂 |

| WAIT_N | 1 | 僂僃僀僩梫媮 | 僆儕僕僫儖CPU偱偼枹巊梡 |

| BREQ_N | 1 | 僶僗巊梡梫媮 | 丂 |

| BACK_N | 1 | 僶僗巊梡嫋壜 | 丂 |

| CS_N[7:0] | 8 | 僄儕傾慖戰 | (専摙拞) |

| NMI_N | 1 | 僲儞丒儅僗僇僽儖妱崬傒 | 丂 |

| IRQ_N[5:0] | 6 | 妱崬傒梫媮 | (杮悢専摙拞) |

| GR_N | 1 | 僔僗僥儉丒儕僙僢僩 | 丂 |

| CLK | 1 | 僔僗僥儉丒僋儘僢僋 | 丂 |

| VCC | ? | 揹尮(5V) | 丂 |

| GND | ? | 僌儔儞僪 | 丂 |

-

徻嵶愝寁偼偙偪傜(岺帠拞)

丒榑棟僔儈儏儗乕僔儑儞

2崋婡(TTL-FPGA屳姺婡)亂TTL斉亃

- 奐敪曽恓

- TTL偲儊儌儕偺傒偱幚尰偡傞丅(CPLD丄FPGA偼巊梡偟側偄丅)

- ALU偼AND丄OR丄XOR丄NOT偱幚尰偡傞丅

(愱梡偺IC偼巊梡偟側偄丅偙偺偨傔丄墘嶼懍搙偺掅壓偼嫋梕偡傞) - 儅僀僋儘丒僾儘僌儔儉惂屼曽幃

- FPGA斉偲摨堦偺婡夿岅偑摦嶌偡傞丅

- 壖憐婡夿傪幚尰偡傞偙偲傪憐掕偟偨傾乕僉僥僋僠儍丅

- 僋儘僗丒僐儞僷僀儔丄僋儘僗丒傾僙儞僽儔偼巊梡偟側偄丅

- 儅僀僋儘丒僾儘僌儔儉偼SVP偵傛傝I2C-ROM傛傝儘乕僨傿儞僌偡傞丅

- IPL偼嵟弶DMA偵傛傝奿擺偟丄SVP偵傛傝I2C-ROM傊奿擺偡傞丅